# QEP3 Service Manual

By Ian Burkinshaw

Nov 2014

## Contents

Introduction Block Diagram Brief Circuit Description Circuit Diagrams Test Jig and Use Card Layout Waveforms for Programming Voltage generator.

### Introduction

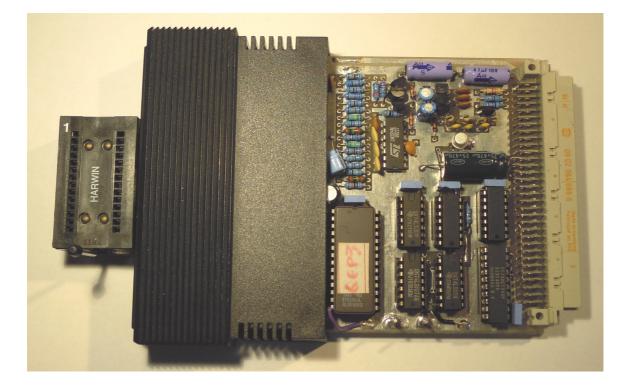

This manual is the result of my investigations after I found my own card had developed a fault. As a result I traced the PCB, which was not easy. But did lead me to a fuller understanding of how this card works.

This manual is designed for people who have some understanding of electronics. If you are unsure then do not attempt to repair your own card, you may do more damage than good. I cannot give 100% guarantee that my work in reverse engineering this card is 100% accurate. But I believe it is not far off. I did get my card card working again.

This manual is provided for guidance only. All errors and omissions are entirely mine. Also any work that you may carry out on your card is entirely at your own risk. No guarantees are provided. Any copyright remains with Care Electronics and/or QUBBESoft P/D

Please also note this quality of the PCB reflects the time in which it was manufactured. Tracks lift ever so easy, so great care is need in replacing any of the none socketed components. The PCB holes are plated though, so do check continuity after carrying out any repair.

Another warning, sorry. DO NOT adjust either of the two pot's unless you have to. These are the two blue devices on the edge of the card next top the Eprom programming socket. Two things could happen, one the 5V supply voltage on the card could go to high and damage chips second your may not be able to blow eproms. I will go into this further later. Not having the original set up information can make this difficult to set correctly.

Warnings and disclaimers now out of the way.

The QEP3 card was originally produced and sold by Care Electronics and in later years was sold by QUBBESoft P/D.

So what is the QEP3 card. It is a Eprom Programmer which plugs into the expansion socket (J1) of a Black Box QL. It can program a limited range of Eprom's.

Eprom Types supported are as follows:-

Do read the User Manual for more user information.

What follows is a block diagram and circuit diagram (3 pages of !) and simplified PCB layouts. Also additional information regarding pin outs of the semiconductor devices used and logic tables.

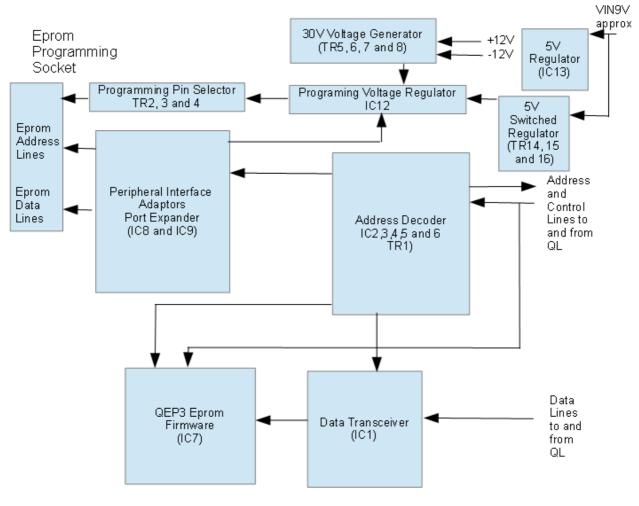

QEP3 Block Diagram

## **Brief Circuit Description**

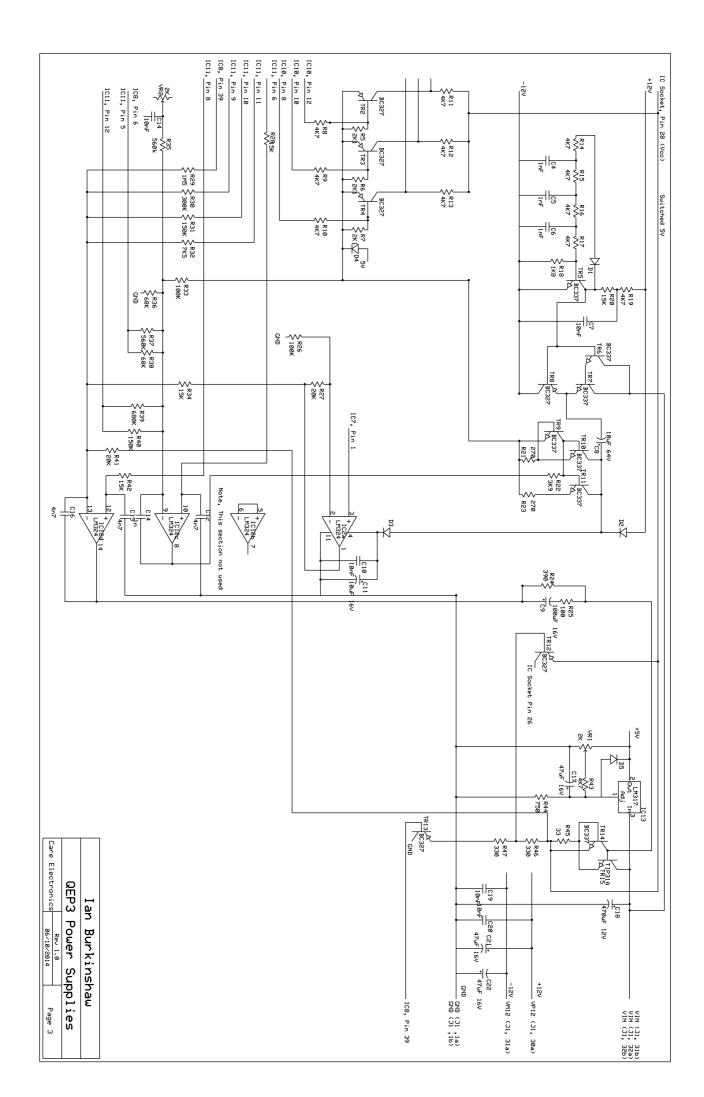

Please read this in conjunction with the block diagram above and the circuit diagrams below. This is not a complete blow by blow account of how the QEP3 programmer works, but should give you a good idea of the basics.

Staring with the power supply sections. IC13 (LM317) adjustable voltage regulator supplies 5V to all the logic IC's (IC1, 2, 3, 4, 5, 6, 7, 8, 9, 10 and 11) This supply is on all the time the unit is powered. The 5V supply is adjustable via VR1, the left hand pot looking from the Eprom socket edge. As already warned DO NOT ADJUST UNLESS ABSOLUTELY NECESSARY. There is a second 5V (TR13, 14 and 15) supply that is switched by the firmware to supply 5v to the Eprom socket. The Eprom socket is only powered when required by the firmware, also this supply will not come on unless an Eprom is properly fitted or the test jig is inserted into the Eprom socket. The firmware checks for the presence of the Eprom in the Eprom socket. More details on the test jig later.

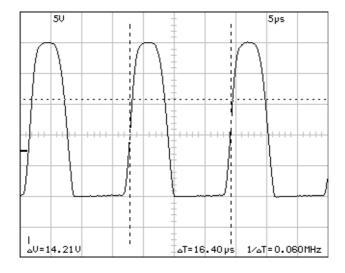

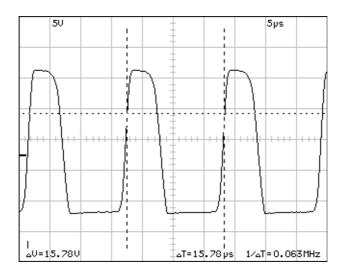

The third and final part of the power supply is the programming voltage generator. This is made up of transistors (TR5, 6, 7 and 8). TR2 with the associate resistors and capacitors make a phase shift oscillator. This runs at a frequency of 60kHz. This feed what can be best described as a power amplifier stage made up of transistors TR6, 7 and 8). The power for this programming voltage generator is provided from the QL's +12V and -12V supplies. So the output after rectification by

diodes D2 and D3 and smoothing by C11 results in 30V to power IC12 which regulates the required programming voltages.

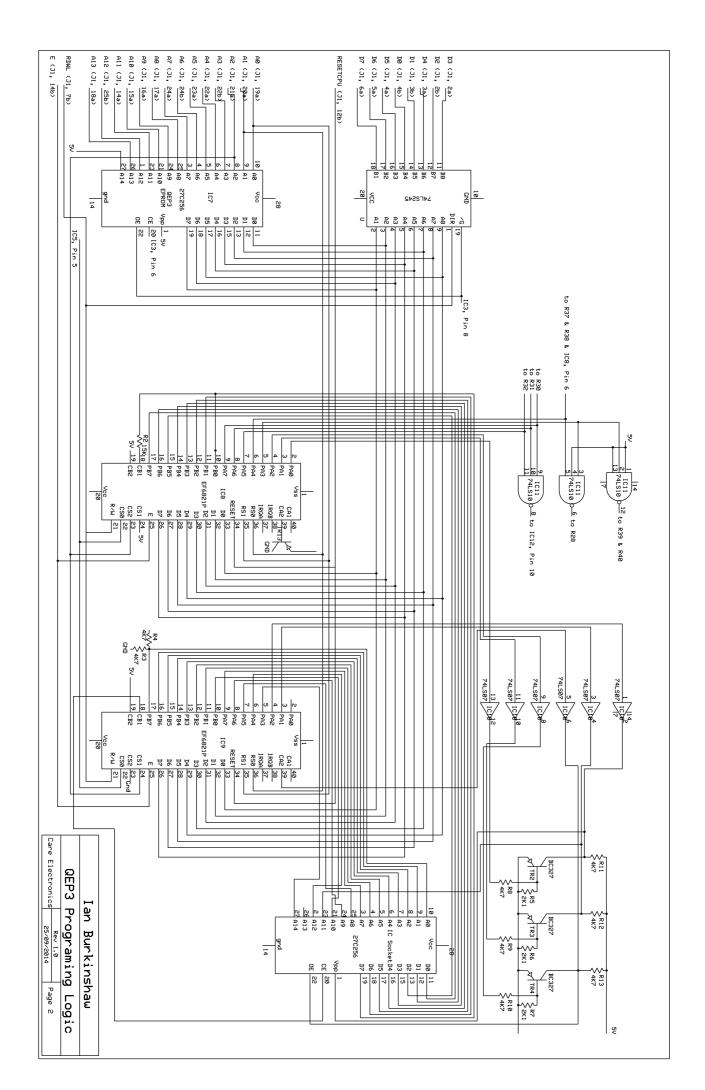

Transistors TR2, 3 and 4 are controlled by the firmware via IC9 and IC10 to select the correct programming pin (not the voltage value) for a given Eprom. The programming voltage comes from the programming voltage generator already described.

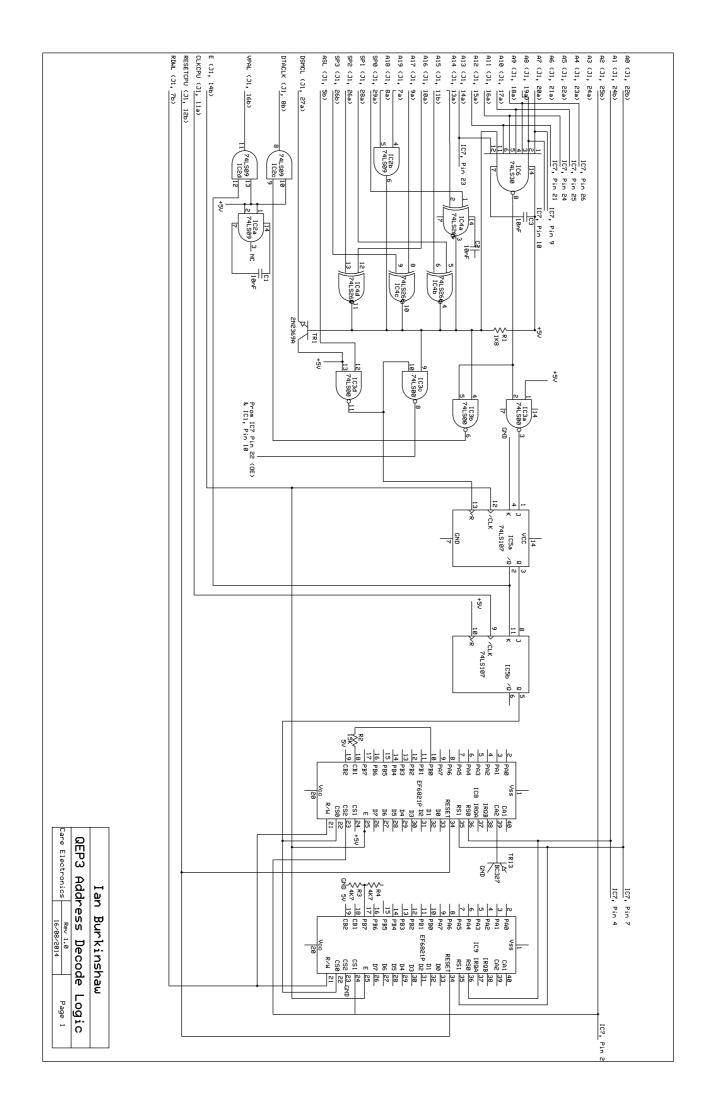

Address decoding and flow control is carried out by IC2, 3, 4, 5, 6 and TR1. The pulse duration is partly controller by the feed back to the QL via TR1 to the DSMCL (Data Strobe – Master Chip) pin . IC5 JK flip flop ensures the correct timing of the address decoding output for IC8 and 9

(Peripheral Interface Adaptor). This done so the the data pins on IC8 and 9 (Peripheral Interface Adaptors) are stable before enabling them.

Note that IC2, 4 and 6 have open collector outputs, that is a pull up resistor is required, which in this case is R1.

Enable control of the 8 bit transceiver device (IC1) is also derived from the address decoder. The directional control of IC1 is derived from the RDWL line from the QL itself.

The two Peripheral Interface Adaptors act as a form of port expanders. Each device provides two 8 bit parallel ports giving a total of four 8 bit ports or if you prefer 32 input/output lines. The ports can be bi directional. In this case only port B on IC8 is used in this manner , these represent the data lines for the Eprom socket, all the others are in output mode only. Data for IC8 and 9 are fed to and from the data transceiver IC1. Also the data lines from the firmware eprom IC7 also are fed via the data transceiver IC1. The outputs PA from IC8 and outputs from IC9 PA and PB are used to provide the address lines to the Eprom sockets and programming voltage selection and programming Eprom pin selection.

The Programming voltage selection is done buy selection of the resistors feeding IC12, this includes VR2 which sets the programming voltage. As already warned DO NOT ADJUST UNLESS ABSOLUTELY NECESSARY. The programming voltage is adjustable via VR2, the right hand pot looking from the Eprom socket edge.

# Test Jig and Use

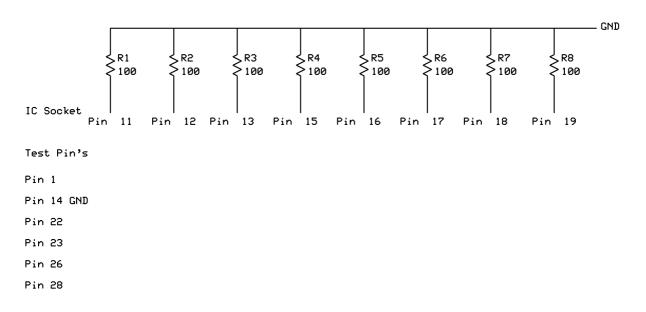

A test jig is required to be able to use the test routine that is contained with the QEP3 firmware. The following circuit needs to be built.

Photo's of such a test jig. Provided as a guide.

The 100 ohm resistors are there to current limit in the event of a fault condition.

To use the jig inset in to the Eprom socket on the QEP3. Turn on the system. Once booted. Under the Options tab select Test. This will than take you thought the following test points.

Pin 28 Low Pin 28 5V Pin 28 3.98V to 4.02V Pin 28 5.98V to 6.02V Pin 26 5.95V to 6.05V Pin 1 Low Pin 1 5.5V to 5.8V Pin 1 12.7V to 12.8V Pin 1 20.8V to 21.2V Pin 1 24.8V to 25.2V Pin 22 Low Pin 22 Low Pin 23 Low Pin 23 24.8V to 25.2V

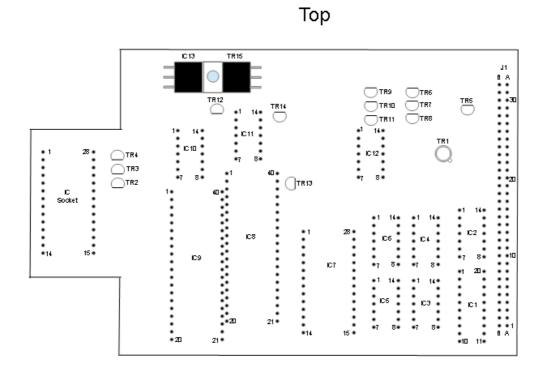

## **Card Layout**

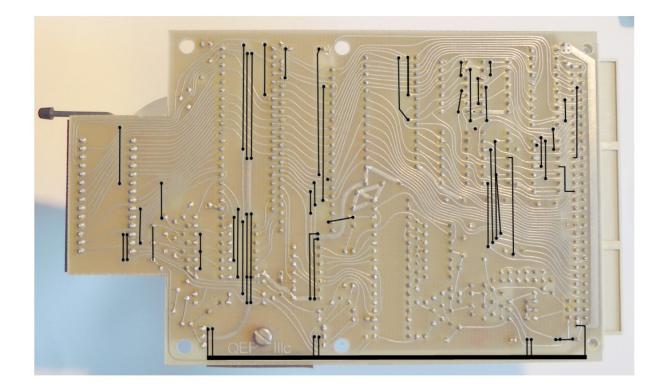

Bottom

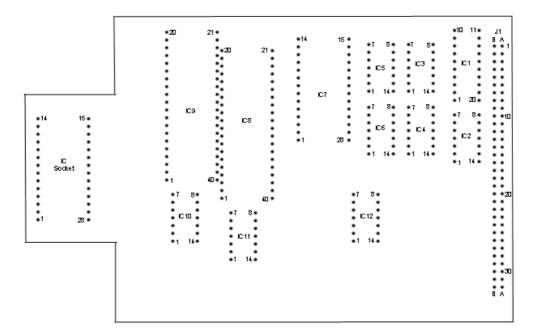

The card is a double sided PCB, the diagram below show the tracks that run on the top of the card as view from below.

Waveforms for the Programming Voltage Generator.

#### **Collector of TR5**

#### Junction of Anode D3 and Cathode D2

Please see associated Excel spread sheet for test results from a fully working card for comparison purposes to aid fault finding.

Data sheets for all the semiconductors use on this card are available from:-

www.datasheetcatalog.com

With the exception of the EF6821P (IC8 and 9) all the semiconductor for this card are available from regular suppliers such as Farnel, RS etc. However the EF6821P's are very hard to come by if at all.